閾值電壓

場效應(yīng)晶體管 (FET) 的閾值電壓通??s寫為 Vth 或 VGS(th),是在源極端子和漏極端子之間形成導(dǎo)電路徑所需的最小柵源電壓 (VGS)。它是保持電源效率的重要比例因子。

當提及結(jié)型場效應(yīng)晶體管 (JFET) 時,閾值電壓通常稱為夾斷電壓。因為應(yīng)用于絕緣柵場效應(yīng)晶體管 (IGFET) 的夾斷是指在高源-漏偏壓下導(dǎo)致電流飽和行為的溝道夾斷,即使電流從未關(guān)閉。與夾斷不同,閾值電壓一詞是明確的,在任何場效應(yīng)晶體管中都指代相同的概念。

晶體管閾值電壓(Threshold voltage):

場效應(yīng)晶體管(FET)的閾值電壓就是指耗盡型FET的夾斷電壓與增強型FET的開啟電壓。

(1)對于JFET:

對于長溝道JFET,一般只有耗盡型的器件;SIT(靜電感應(yīng)晶體管)也可以看成為一種短溝道JFET,該器件就是增強型的器件。

(2)對于MOSFET:

*增強型MOSFET的閾值電壓VT是指剛剛產(chǎn)生出溝道(表面強反型層)時的外加?xùn)烹妷骸?/div>

①對于理想的增強型MOSFET(即系統(tǒng)中不含有任何電荷狀態(tài),在柵電壓Vgs = 0時,半導(dǎo)體表面的能帶為平帶狀態(tài)),閾值電壓可給出為VT = ( SiO2層上的電壓Vi ) + 2ψb = -[2εεo q Na ( 2ψb )] / Ci + 2ψb ,式中Vi ≈ (耗盡層電荷Qb) / Ci,Qb =-( 2εεo q Na [ 2ψb ] ),Ci是單位面積的SiO2電容,ψb是半導(dǎo)體的Fermi勢(等于本征Fermi能級Ei與Ef之差)。

②對于實際的增強型MOSFET,由于金屬-半導(dǎo)體功函數(shù)差φms 和Si-SiO2系統(tǒng)中電荷的影響, 在Vgs = 0時半導(dǎo)體表面能帶即已經(jīng)發(fā)生了彎曲,從而需要另外再加上一定的電壓——“平帶電壓”才能使表面附近的能帶與體內(nèi)拉平。

因為金屬-半導(dǎo)體的功函數(shù)差可以用Fermi勢來表示:φms = (柵金屬的Fermi勢ψG )-(半導(dǎo)體的Fermi勢ψB ) ,ψb = ( kT/q ) ln(Na/ni) ,對多晶硅柵電極(通常是高摻雜),ψg≈±0.56 V [+用于p型, -用于n型柵]。而且SiO2/Si 系統(tǒng)內(nèi)部和界面的電荷的影響可用有效界面電荷Qf表示。從而可給出平帶電壓為 Vfb = φms-Qf /Ci 。

所以,實際MOSFET的閾值電壓為VT = -[2εεo q Na ( 2ψb )] /Ci + 2ψb +φms-Qf /Ci 。

進一步,若當半導(dǎo)體襯底還加有反向偏壓Vbs時,則將使溝道下面的耗盡層寬度有一定的增厚, 從而使閾值電壓變化為:VT = -[2εεo q Na ( 2ψb+Vbs )] /Ci + 2ψb +φms-Qf /Ci 。

在制造MOSFET時,為了獲得所需要的VT值和使VT值穩(wěn)定,就需要采取若干有效的技術(shù)措施;這里主要是控制Si-SiO2系統(tǒng)中電荷Qf :其中的固定正電荷(直接影響到VT值的大小) 與半導(dǎo)體表面狀態(tài)和氧化速度等有關(guān)(可達到<1012/cm2); 而可動電荷 (影響到VT值的穩(wěn)定性) 與Na+等的沾污有關(guān)。因此特別需要注意在氧化等高溫工藝過程中的清潔度。

*耗盡型MOSFET的閾值電壓VT是指剛好夾斷溝道時的柵極電壓。情況與增強型器件的類似。

(3)對于BJT,閾值電壓VTB是指輸出電流Ic等于某一定值Ict (如1mA) 時的Vbe值。由VTB = (kT/q) ln(Ict/Isn) 得知:a)凡是能導(dǎo)致Ic發(fā)生明顯變化的因素 (如摻雜濃度和結(jié)面積等),卻對VTB影響不大,則BJT的VTB可控性較好;b) VTB 對于溫度很敏感,將隨著溫度的升高而靈敏地降低,則可用VTB值來感測溫度。

閾值電壓有哪些影響因素?

第一個影響閾值電壓的因素是作為介質(zhì)的二氧化硅(柵氧化層)中的電荷Qss以及電荷的性質(zhì)。這種電荷通常是由多種原因產(chǎn)生的,其中的一部分帶正電,一部分帶負電,其凈電荷的極性顯然會對襯底表面產(chǎn)生電荷感應(yīng),從而影響反型層的形成,或者是使器件耗盡,或者是阻礙反型層的形成。Qss通常為可動正電荷。

第二個影響閾值電壓的因素是襯底的摻雜濃度。要在襯底的上表面產(chǎn)生反型層,必須施加能夠?qū)⒈砻婧谋M并且形成襯底少數(shù)載流子的積累的柵源電壓,這個電壓的大小與襯底的摻雜濃度有直接的關(guān)系。襯底摻雜濃度(QB)越低,多數(shù)載流子的濃度也越低,使襯底表面耗盡和反型所需要的電壓VGS越小。

所以,襯底摻雜濃度是一個重要的參數(shù),襯底摻雜濃度越低,器件的閾值電壓數(shù)值將越小,反之則閾值電壓值越高。對于一個成熟穩(wěn)定的工藝和器件基本結(jié)構(gòu),器件閾值電壓的調(diào)整,主要通過改變襯底摻雜濃度或襯底表面摻雜濃度進行。襯底表面摻雜濃度的調(diào)整是通過離子注入雜質(zhì)離子進行。

第三個影響閾值電壓的因素是由柵氧化層厚度tOX決定的單位面積柵電容的大小。單位面積柵電容越大,電荷數(shù)量變化對VGS的變化越敏感,器件的閾值電壓則越小。實際的效應(yīng)是,柵氧化層的厚度越薄,單位面積柵電容越大,相應(yīng)的閾值電壓數(shù)值越低。但因為柵氧化層越薄,氧化層中的場強越大,因此,柵氧化層的厚度受到氧化層擊穿電壓的限制。

選用其他介質(zhì)材料做柵介質(zhì)是當前工藝中的一個方向。例如選用氮氧化硅 SiNxOy 替代二氧化硅是一個微電子技術(shù)的發(fā)展方向。正在研究其它具有高介電常數(shù)的材料,稱為高k柵絕緣介質(zhì)。

第四個對器件閾值電壓具有重要影響的參數(shù)是柵材料與硅襯底的功函數(shù)差ΦMS的數(shù)值,這和柵材料性質(zhì)以及襯底的摻雜類型有關(guān),在一定的襯底摻雜條件下,柵極材料類型和柵極摻雜條件都將改變閾值電壓。對于以多晶硅為柵極的器件,器件的閾值電壓因多晶硅的摻雜類型以及摻雜濃度而發(fā)生變化。

可見,在正常條件下,很容易得到增強型PMOS管。為了制得增強型NMOS管,則需注意減少Q(mào)ss、Qox,增加QB。采用硅柵工藝對制做增強型NMOS管和絕對值小的增強型PMOS管有利。

溫度對閾值電壓的影響

溫度對晶體管閾值電壓的影響是一種重要的影響因素,其影響的原因是由于溫度的變化會導(dǎo)致材料本身的物理特性發(fā)生變化。

在晶體管的工作中,閾值電壓是指控制電壓與柵極電壓之差,達到這個電壓值后晶體管就開始導(dǎo)通。隨著溫度的變化,導(dǎo)體的電阻會發(fā)生變化,從而影響到柵極電壓的大小,同時材料的電子特性也會發(fā)生變化,從而影響到閾值電壓的大小。

一般來說,當溫度升高時,閾值電壓會降低,這意味著控制電壓與柵極電壓之差變小,晶體管容易被激發(fā)進入導(dǎo)通狀態(tài),從而會增加功耗和熱量。因此,在設(shè)計中需要考慮溫度對閾值電壓的影響,并對芯片進行充分的溫度測試和特性化,以保證芯片在不同溫度下的正常工作。

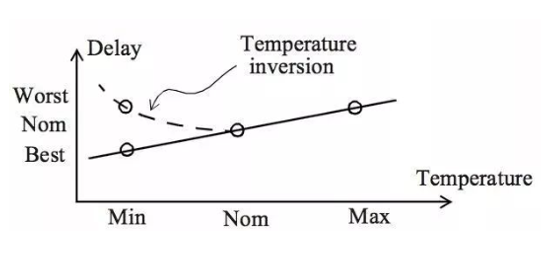

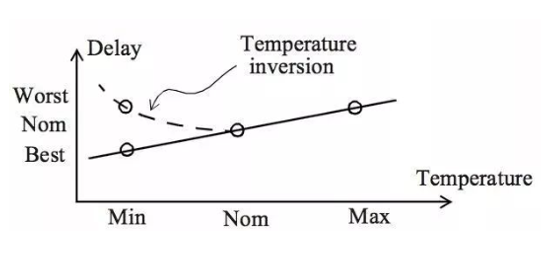

IC芯片必須適應(yīng)溫度不恒定的環(huán)境,當芯片運行時,由于開關(guān)功耗、短路功耗和漏電功耗會使芯片內(nèi)部的溫度發(fā)生變化。溫度波動對性能的影響通常被認為是線性的,通常對于一個管子,當溫度升高,空穴/電子的遷移率會變慢(晶格振動散射對載流子的影響越來越強),使延時增加。

注意溫度翻轉(zhuǎn)效應(yīng):

但在深亞微米,溫度對性能的影響會導(dǎo)致一種溫度反轉(zhuǎn)現(xiàn)象,因為溫度的升高也會使管子的閾值電壓降低,較低的閾值電壓意味著更高的電流,因此管子的延時減小,而在溫度較低時,閾值電壓帶來的變化對性能的影響更大,因此器件會出現(xiàn)一段性能隨溫度下降的曲線,之后再隨溫度上升,至于溫度翻轉(zhuǎn)點跟具體的工藝相關(guān)。

這里可以理解為深亞微米工藝在較低溫度時,閾值電壓降低帶來的daley變化占主導(dǎo)。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280

- 上一篇:mos管n溝道和p溝道的區(qū)別介紹

- 下一篇:最后一頁

相關(guān)閱讀